Testpads: Difference between revisions

Jump to navigation

Jump to search

JTAG pins and UART-A ball names |

Notes on JTAG and lockout |

||

| Line 59: | Line 59: | ||

=== Cluster C === | === Cluster C === | ||

The JTAG pins are multiplexed between NV_JTAG and ARM_JTAG by the TRST pin: | |||

* NV_JTAG contains a single TAP (ID 0x221173D7) for boundary scan board verification. | |||

* ARM_JTAG contains two debugging TAPs for CoreSight (ID 0x5BA00477) and BPMP (ID 0x4F1F0F0F). | |||

Note: NV_JTAG and ARM_JTAG are locked out by [[Fuses#Cache|FUSE_ARM_JTAG_DIS]] on production devices. | |||

{| class=wikitable | {| class=wikitable | ||

| Line 71: | Line 77: | ||

| 4 || JTAG_TCK || || 0-1.8V || || || | | 4 || JTAG_TCK || || 0-1.8V || || || | ||

|- | |- | ||

| 5 || JTAG_RTCK || || 0-1.8V || || || | | 5 || JTAG_RTCK || || 0-1.8V || || || Unused for NV_JTAG | ||

|- | |- | ||

| 6 || UART1_RTS || || 0-1.8V || || || UART-A RTS Flow control | | 6 || UART1_RTS || || 0-1.8V || || || UART-A RTS Flow control | ||

| Line 81: | Line 87: | ||

| 9 || JTAG_TMS || || 0-1.8V || || || | | 9 || JTAG_TMS || || 0-1.8V || || || | ||

|- | |- | ||

| 10 || JTAG_TRST_N || || 0-1.8V || || || | | 10 || JTAG_TRST_N || || 0-1.8V || || || Not a TAP reset; Multiplexes between NV_JTAG (HI) and ARM_JTAG (LO) | ||

|- | |- | ||

| 11 || +1.8V || || 0-1.8V || || || | | 11 || +1.8V || || 0-1.8V || || || | ||

Revision as of 09:15, 15 May 2021

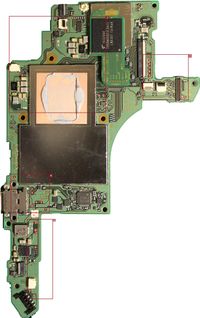

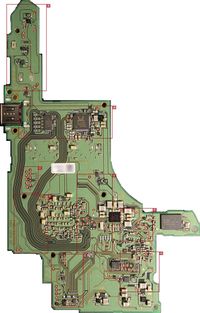

The Nintendo Switch mainboard has a series of testpads on the front and back, presumably used in factory test, diagnostics, and early board bringup procedures.

Raw Logic captures

These are reference materials, taken from poking at I/O on various testpads. https://github.com/hedgeberg/Switch-Logic-Captures

Photos

Pinouts

Cluster A

| Pad # | Name | Type | Levels | Continuity | Frequency | Comment |

|---|---|---|---|---|---|---|

| 1 | Batt GND? | |||||

| 2 | Battery pulse? | Pulse train | 0-3.3V | L-5? | ||

| 3 | Battery Vdd | |||||

| 4 | Speaker R + | Square wave | 0-3.3V | Speaker Right + | ||

| 5 | Speaker R - | Square wave | 0-3.3V | Speaker Right - | ||

| 6 | Weak GND? | |||||

| 7 | SDA | I2C | 0-1.8V | I2C Port 0 | ||

| 8 | SCL | I2C | 0-1.8V | I2C Port 0 | ||

| 9 | USB-PWR-WAVE? | Square wave | 0-3.3V | K-4, K-5? | ~11 Hz | |

| 10 | USB-PWR-WAVE? | Square wave | 0-3.3V | K-4, K-5? | ~11 Hz |

Cluster B

| Pad # | Name | Type | Levels | Continuity | Frequency | Comment |

|---|---|---|---|---|---|---|

| 1 | DBVDD | from ALC5639 pin 43 | ||||

| 2 | D+ | USB-C | Cluster B - 3 | |||

| 3 | D- | USB-C | Cluster B - 2 | |||

| 4 | +3.3V | XRST | from M92T36 pin 4 | |||

| 5 | +3.3V | VSVR | from M92T36 pin 6 | |||

| 5(b) | VUSB | VB | from M92T36 pin 9 | |||

| 6 | GND |

Cluster C

The JTAG pins are multiplexed between NV_JTAG and ARM_JTAG by the TRST pin:

- NV_JTAG contains a single TAP (ID 0x221173D7) for boundary scan board verification.

- ARM_JTAG contains two debugging TAPs for CoreSight (ID 0x5BA00477) and BPMP (ID 0x4F1F0F0F).

Note: NV_JTAG and ARM_JTAG are locked out by FUSE_ARM_JTAG_DIS on production devices.

| Pad # | Name | Type | Levels | Continuity | Frequency | Comment |

|---|---|---|---|---|---|---|

| 1 | JTAG_TDI | 0-1.8V | ||||

| 2 | UART1_RX | 0-1.8V | UART-A RX | |||

| 3 | UART1_TX | 0-1.8V | UART-A TX | |||

| 4 | JTAG_TCK | 0-1.8V | ||||

| 5 | JTAG_RTCK | 0-1.8V | Unused for NV_JTAG | |||

| 6 | UART1_RTS | 0-1.8V | UART-A RTS Flow control | |||

| 7 | JTAG_TDO | 0-1.8V | ||||

| 8 | UART1_CTS | 0-1.8V | UART-A CTS Flow control | |||

| 9 | JTAG_TMS | 0-1.8V | ||||

| 10 | JTAG_TRST_N | 0-1.8V | Not a TAP reset; Multiplexes between NV_JTAG (HI) and ARM_JTAG (LO) | |||

| 11 | +1.8V | 0-1.8V |

Cluster D

| Pad # | Name | Type | Levels | Continuity | Frequency | Comment |

|---|---|---|---|---|---|---|

| 1 | GND | |||||

| 4 | Seaker L + | Speaker Left + | ||||

| 5 | Seaker L - | Speaker Left - |

Cluster E

| Pad # | Name | Type | Levels | Continuity | Frequency | Comment |

|---|---|---|---|---|---|---|

| 1 | Vol (-) | Button Vol (-) | ||||

| 10 | Reset | |||||

| 11 | Power Button | Pushbutton | 4V-0V | Active low |

Cluster G

| Pad # | Name | Type | Levels | Continuity | Frequency | Comment |

|---|---|---|---|---|---|---|

| 1 | SD card detect | |||||

| 2 | GND | |||||

| 4 | Vol(+) | Button Vol (+) | ||||

| 5 | Li-Ion Batt Vdd Mirror | Power Supply | ||||

| 9 | BUTTON_HOME | RCM strap |

Cluster H

| Pad # | Name | Type | Levels | Continuity | Frequency | Comment |

|---|---|---|---|---|---|---|

| 1 | ||||||

| 2 | ||||||

| 3 | ||||||

| 4 | Screen_on | On/Off | 0-1.8v | I-2 | Screen power state, active high | |

| 5 | Flow control | 0-1.8V | I-5 | Flow control for pad I-4? | ||

| 6 | ||||||

| 7 | UART | 0-1.8V | I-4 | 1.5MBaud? | ||

| 8 | UART | 0-1.8V | I-3 | 1.5MBaud? | ||

| 9 | ||||||

| 10 | H-12 | On the same trace | ||||

| 11 | Goes to a small ceramic cap near WiFi/BT IC? | |||||

| 12 | H-10 | On the same trace |

Cluster I

| Pad # | Name | Type | Levels | Continuity | Frequency | Comment |

|---|---|---|---|---|---|---|

| 1 | GND | |||||

| 2 | Screen_on | On/Off | 0-1.8V | Screen power state, active high | ||

| 3 | UART | 0-1.8V | 1.5MBaud? | Communication CPU -> Bluetooth using HCI | ||

| 4 | UART | 0-1.8V | 1.5MBaud? | Communication Bluetooth -> CPU using HCI | ||

| 5 | Flow control | 0-1.8V | Flow control for pad I-4? | |||

| 6 | 0-1.8V | Needs testing with chip/touch screen interface board plugged in |

Cluster J

| Pad # | Name | Type | Levels | Continuity | Frequency | Comment |

|---|---|---|---|---|---|---|

| 1 | ? | Edge | 0-1.8V | Turns on around same time as pad J-3 | ||

| 2 | GND | |||||

| 3 | ? | Edge | 0-1.8V | Turns on around same time as pad J-1, slightly after | ||

| 4 | Power button | Pushbutton | 4V-0V | Active low | ||

| 5 | ? | Constant? | 0V | Ground?-NT | ||

| 6 | ? | Edge | 0-1.8V | Turns on with pad J-6, ~1s after J-1/J-3 | ||

| 7 | ? | Edge | 0-1.8V | Turns on with pad J-5, ~1s after J-1/J-3 | ||

| 8 | ? | Edge? | 0-1.8V | Turns on ~1s after J-6/J-7, turns off at unknown point |

Cluster K

| Pad # | Name | Type | Levels | Continuity | Frequency | Comment |

|---|---|---|---|---|---|---|

| 1 | GND | |||||

| 2 | D- | USB-C | Cluster B - 3 | |||

| 3 | D+ | USB-C | Cluster B - 2 | |||

| 4 | USB-PWR-WAVE? | Square wave | 0V-3.3V | A-9, A-10? | ~11 Hz | |

| 5 | USB-PWR-WAVE? | Square wave | 0V-3.3V | A-9, A-10? | ~11 Hz | Appears to mirror K4. Duty cycle 66.67%. Low on screen lock. Off until first interaction. |

| 6 | USB-C V+ | Supply power | support fast charger : "normal mode = 5V+" "Fast changer = 12V+" | |||

| 7 | BQ24193 VBUS + M92T36 VEX | Power supply? | ~3V-0V | None known | N/A | 0 when usb-c not plugged in, falls slowly on first interaction if USB-C plugged in. Power draw related? |

Cluster L

TODO: Update diagram

| Pad # | Name | Type | Levels | Continuity | Frequency | Comment |

|---|---|---|---|---|---|---|

| 1 | Li-Ion Batt Vdd Mirror | Power Supply | Std. Li-Ion | |||

| 2 | GND | |||||

| 3 | Li-Ion Batt Vdd | Battery Input | Std. Li-Ion | |||

| 4 | Mirrored Ground? | Holds steady @ 0, looks like a decoupled isolated ground | ||||

| 5 | Battery pulse? | <1 Hz | Duty cycle ~0% | |||

| 6 | GND |